ADVERTISEMENT

因應人工智慧相關應用以及未來趨勢,Arm 於今年 Computex 展期發表 big.LITTLE 下一代的 DynamIQ 多核架構,前幾日則是公布 DynamIQ 影片,影片中使用動畫效果對 DynamIQ 做出更清楚的解釋,也指出與 big.LITTLE 的不同或是混用的情境狀態。

big.LITTLE 異質多核心架構已應用在 Arm 處理器多年,大家也已經很熟悉,適用的處理器核心從 Cortex-A7、Cortex-A15 到近期支援 64 位元指令集的 Cortex-A53、Cortex-A73,單一 big 或是 LITTLE 叢集可以塞入最多 4 個相同架構與快取的核心,各叢集各自擁有 1 組叢集內部核心共享的 L2 快取,叢集內部核心可以動態調整電壓與頻率,但是各核心必須相同;叢集之間透過 Cache Coherent Interconnect 相互連接,透過排程器依據各核心負載狀況以及運算量調整各個核心的工作,或甚至在不同叢集間遷移工作,這就是目前大家熟悉的 big,LITTLE。

▲1 組典型的 big.LITTLE 系統。

新的 DynamIQ 以 big.LITTLE 為技術基底,改良 big.LITTLE 的不足,譬如 DynamIQ 的 1 組叢集最高可放入 8 個核心(目前相容 DynamIQ 的處理器核心為 Cortex-A75、Cortex-A55),製造商可以任意組合核心,譬如 1+7 或是 2+6 的形式,但是單一叢集大核心最高限制僅能 4 核。

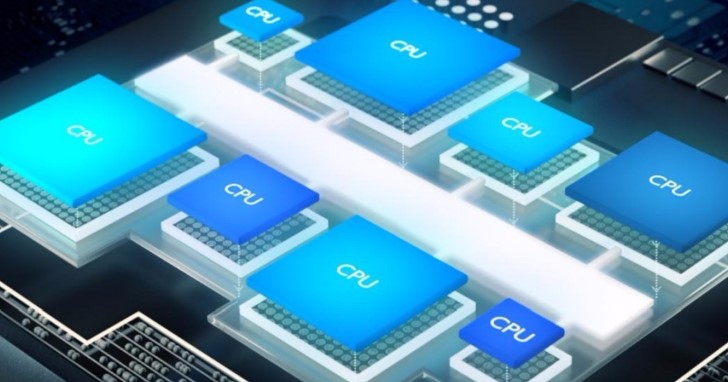

各核心微架構、快取容量、時脈高低、電源狀態也不必相同,因此若未來 Arm 推出新款相容 DynamIQ 的處理器核心,我們就可以見到單一叢集內部擁有 3 種以上的處理器微架構。整個叢集分享 1 組共用的 L3 快取,或是依照 Arm 的技術文件,單一叢集使用 DynamIQ Shared Unit 將所有核心連結在一起,提供更快的執行緒遷移,再透過 Cache Coherent Interconnect 與 SoC 內部其它功能區塊相互連接。透過 Cache Coherent Interconnect,也能夠和其它運算功能區塊,如 Mali 繪圖核心,組成異質運算架構。

▲1 組 DynamIQ 叢集。

▲big.LITTLE 與 DynamIQ big.LITTLE 架構差異性。

▲DynamIQ 也可以完全不使用 big.LITTLE 大小核組合方式,僅以單一微架構核心組成。

▲Arm DynamIQ 介紹影片。

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!