據報導,AMD 正在兩個不同的代工節點上製造即將推出的"Zen 5"和"Zen 5c"CPU核心晶片(CCD),為即將推出的Ryzen"Granite Ridge"桌機處理器、"Fire Range"移動處理器和EPYC"Turin"伺服器處理器提供基礎的Zen 5 CCD將在4奈米EUV代工節點上製造,這一節點比該公司目前製造"Zen 4"CCD的5奈米EUV節點稍先進一些。

另一方面,"Zen 5c"CCD,或高密度組態純"Zen 5c"核心的晶片組,將在更先進的 3 奈米 EUV 代工節點上製造。這兩種 CCD 都將在 2024 年第二季度投入量產,預計下半年推出產品。

"Zen 5c"晶片組擁有龐大的 32 個核心,分佈在兩個各有 16 個核心的 CCX 中。每個 CCX 有 16 個核心,共享 32 MB 三級快取。這 32 個核心每個都有 1 MB 的二級快取,總共 64 MB 的三級快取,這就是 AMD 轉向 3 奈米代工節點的原因。

另一個原因可能是電壓,"Zen 5c"核心可以被看成"Zen 5"的高度緊湊型變體,它的工作電壓帶低於其較大的兄弟型號,但 IPC 或指令集沒有任何變化。

採用 3 奈米製程的決定可能是為了在較低的電壓下提高時鐘速度,以便在 IPC 和核心數量之外,利用時鐘速度提高性能。

採用"Zen 5c"晶片組的EPYC處理器將採用不超過 6 個這樣的大型 CCD,最大核心數為 192 個。普通的"Zen 5"CCD 在單個 CCX 中僅有 8 個核心,核心之間共享 32 MB L3 快取記憶體;TSV 提供 3D 垂直快取記憶體,以便在特殊型號中增加 L3 快取記憶體。

在AMD Zen 5架構平台中,最關鍵的核心運算晶片是由台積電以3奈米製程製造。此外,HPC 平台 MI300 系列也已投入量產,採用台積電的 4 奈米和 5 奈米工藝。訂單勢頭有增無減,台積電今年從 AMD獲得的先進製程訂單勢頭非常強勁。

業內分析認為,3 奈米技術的量產需要相對較長的時間。據估計,AMD 新的 3nm Zen 5 架構平台將在第二季度左右進入晶圓量產階段。屆時,產能有望逐月提升。

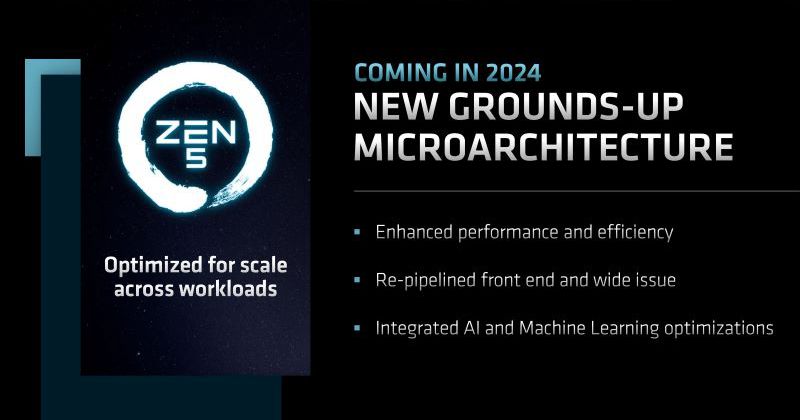

目前,關於 AMD Zen 5 核心架構的資訊還不是很多,但從該公司的官方聲明來看,它將提供更多的功能:

-

提高性能和效率

-

前端重新管道化和寬幅問題

-

內建人工智慧和機器學習最佳化

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!