ADVERTISEMENT

為了在更小的封裝裡塞入更多電晶體提升運算效能,現今製造商都會利用 3D 堆疊方式透過矽穿孔技術,將多層晶粒連結在一起。但是傳統的散熱片或是水冷頭已不符合解熱需求,被夾在中間的晶粒往往無法及時冷卻,因而限制提升效能的空間。

為了替高效能晶片移除運作時產生的廢熱,傳統作法將具有一定鰭片數量的金屬緊貼晶片本身,利用高導熱係數金屬將晶片廢熱導出,再透過空氣流經大面積鰭片帶走廢熱。水冷系統運作原理也是如此,只不過在高導熱係數金屬和空氣之間再多加 1 層冷卻液,利用液體流動循環方式將廢熱運載至表面積更大的水冷排,再將熱量排放至空氣當中。

過往為了提升單一晶片晶粒的運算效能,除了提升運作時脈之外,另一種方式就是微縮製程放入更多的電晶體,可惜製程微縮有其極限,各家製造商也都不斷地研究新材料尋求突破。另一方面,3D 堆疊則被視為能夠有效地提升單位面積運作效能的技術,利用矽穿孔將多層晶粒相互連接,堆疊數層也就相當於提升數倍的電晶體數量。

3D 堆疊技術封裝技術需要克服封裝良率問題之外,還需要解決多個高效能晶粒堆疊在一起的散熱問題。若是採用一般金屬導熱方式,僅有位於封裝最上層的晶粒受惠,其它類似夾心餅乾內層的晶粒就無法有效排出廢熱,堆積熱量產生熱點的結果就是導致產品損毀。因此目前 3D 堆疊技術大多將負責運算的晶粒擺在最上層,中間放置比較不熱的記憶體或是其它連結用載板(interposer)。

▲博士生 Kevin Drummond 手持內建微水道的晶片原型。

美國國防部 DARPA(Defense Advanced Research Projects Agency)從 2013 年就資助普渡大學進行研究,目標是能夠解決每平方公分產生 1000W 廢熱,以便應付如雷達電子產品或是高性能超級電腦的需求。經過為期 4 年的研究,最終在該校的 Birck 奈米科技中心製造出符合 DARPA 要求的原型產品。

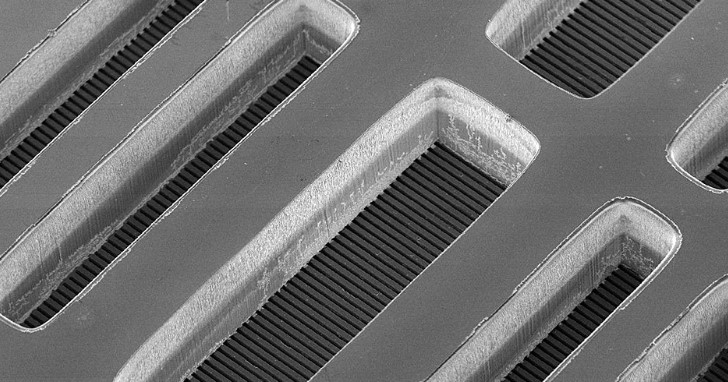

該晶片內部整合了多條寬度 10~15 微米,深度 300 微米的水道,且為了提供足夠的液體流量,採用特殊的多階層水道設計,而非 1 根腸子通到底設計方式,將冷卻液體分別運輸到不同的區域。注入該水道的液體為 HFE-7100,主要成分為 C4F9OCH3,具備不導電的特性,流經水道時會受熱變為汽態,由液相-汽相轉換帶走晶粒產生的熱。

該報導並未明確指出實際商業化階段或是未來展望,但可以確定的是該技術並不會那麼快就出現在市面上。如同我們先前報導的 Sandia National Laboratories 所研究的散熱器一樣,今年才由 Thermaltake 推出 Engine 27,而且運作時的聲響還不小,擁有獨特的金屬材質風切聲。

資料來源

Purdue develops ‘intrachip’ micro-cooling system for high-performance radar, supercomputers

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!