ADVERTISEMENT

應用材料公司(Applied Materials)宣布推出新系統產品,藉由新的電晶體佈線工程設計,大幅降低電阻,讓影響晶片效能與功率的重大瓶頸迎刃而解。

主流晶片廠商正在運用微影技術,將晶片縮小至 3 奈米和以下節點,但是導線越細,電阻便會以倍數增加,導致晶片效能降低,並增加耗電量。若放任佈線電阻的問題不管,先進電晶體的優勢可能會蕩然無存。

應材公司指出,製作晶片時必須將佈線沉積到介電材料上的蝕刻導孔和溝槽,而傳統的方法是使用金屬疊層進行沉積,包含避免金屬與介電材料混合的阻障層、可增加附著力的襯墊層、幫助金屬填充的晶種層,以及電晶體接點所用的鎢或鈷和導線所用的銅等導電金屬。由於阻障層與襯墊層的微縮效果不佳,因此當導孔和溝槽縮小時,導電金屬可用的空間比例也會降低,而佈線越小,電阻就越大。

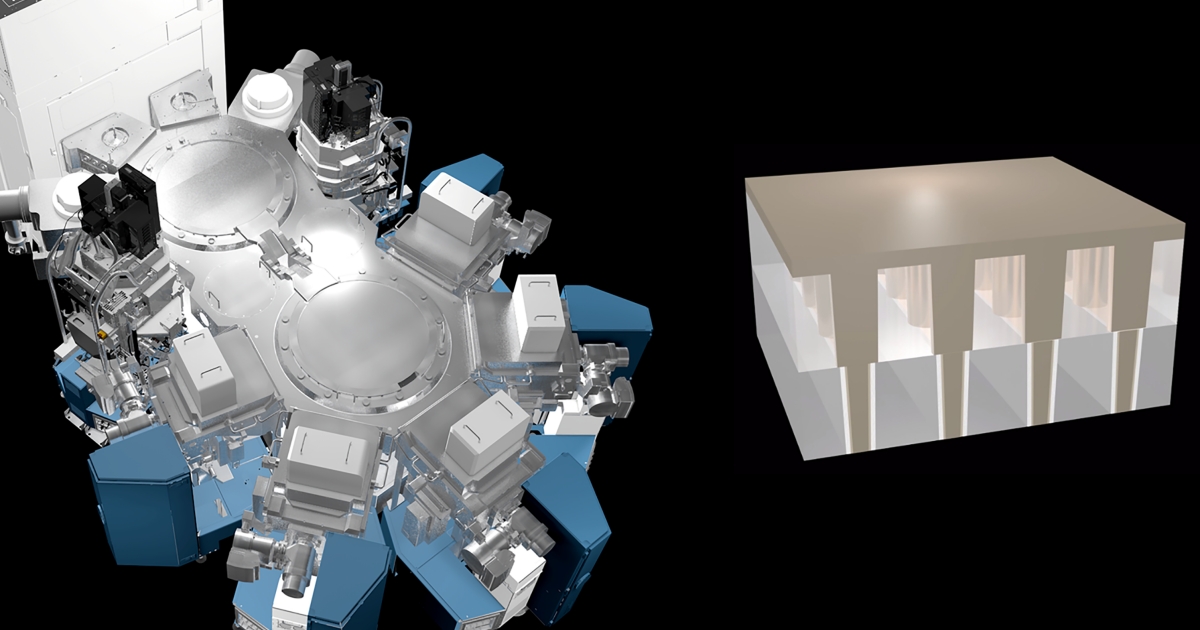

應材公司推出的 Ioniq PVD 系統是整合性材料解決方案(Integrated Materials Solutions)的產品,在高真空環境下將表面處理與物理氣相沉積(PVD)和化學氣相沉積(CVD)製程整合在同一套系統。

透過 Ioniq PVD 系統,晶片廠商可以將使用氮化鈦製造的高電阻率襯墊層與阻障層,替換成使用 PVD 沉積的低電阻率鎢膜,並結合使用 CVD 沉積的鎢膜,形成純鎢的金屬接點。這項解決方案進而解決電阻問題,讓 2D 微縮技術持續應用在 3 奈米和以下的節點。

應用材料公司資深副總裁暨半導體產品事業群總經理帕布‧若傑(Prabu Raja)博士表示,創新的 Ioniq PVD 系統產品解決了影響電晶體效能的重大瓶頸,不僅能提升運作速度,還能降低功率耗損。

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!