中國科學院計算技術研究所的研究人員在《Fundamental Research》雜誌上發表了一篇論文討論了曝光機和小晶片的侷限性,稱之為「大晶片」的架構,也介紹了一個基於16個chiplet的256核處理器系統,命名為「浙江大晶片」,並表示未來這種設計可以擴展到100個芯粒,從而達成1600核心。

根據報導, 「浙江大晶片」採用22nm製造工藝,推測來自中芯國際,因為延遲非常低,整體性能不俗的同時,功耗並不高。

由16個小晶片組成, 每個小晶片中都有16 個CPU 處理器,透過晶片網路(NOC) 連接,每個tile 完全對稱互連,以實現多個chiplet 之間的通訊。CPU處理器是基於RISC-V指令集設計的。此外,該處理器採用統一記憶體系統,這意味著任何tile上的任何核心都可以直接存取整個處理器的記憶體。

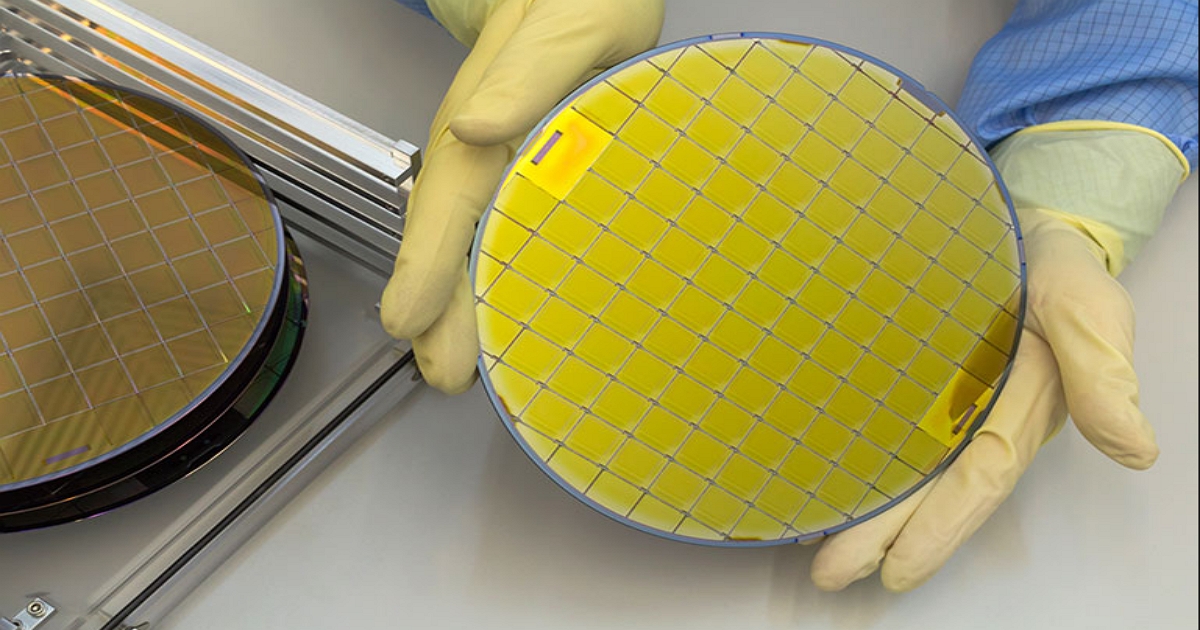

以下是如何使用中介層將 16 個小晶片捆綁在一起形成具有共享記憶體的 256 核計算複合體,從而實現晶片間 (D2D) 互連:

CAS 研究人員表示,為了連接多個小晶片,採用了晶片間 (D2D) 介面。此介面採用基於時分復用機制的通道共享技術進行設計。這種方法減少了晶片間訊號的數量,從而最大限度地減少了 I/O 凸塊和內插器佈線資源的面積開銷,從而可以顯著降低基板設計的複雜性。

雖然一個大晶片計算引擎作為多晶片或晶圓級複合體可能很有趣,但重要的是如何將這些設備互連以提供百億億級計算系統。

值得一提的是,早在2019年,半導體企業Cerebras Systems就發表了世界最大晶片「WSE」(Wafer Scale Engine),一顆如同晶圓大小的AI處理器。採用台積電16nm製程製造,擁有46225平方毫米麵積、1.2兆個電晶體、40萬個AI核心、18GB SRAM快取、9PB/s記憶體頻寬、100Pb/s互連頻寬,功耗也高達15千瓦。

- 延伸閱讀:傳中芯國際正在用DUV打造5奈米技術,良品率大約僅30-40%成本高昂

- 延伸閱讀:當年說良率要趕上台積電,中芯國際官網「14奈米」代工方案默默下架

- 延伸閱讀:中芯國際稱14奈米製程良率達95%追上台積電?專家表示質疑

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!