ADVERTISEMENT

HBM 高頻寬記憶體走向與傳統記憶體相當不同,後者依舊以提升 I/O 傳輸時脈做為增加存取頻寬的手段,HBM 則是以更寬的匯流排平行處理,單一堆疊採用 1024bit,如今 JEDEC 釋出更新版 JESD235B,同步提升容量與速度。

HBM(High Bandwidth Memory)高頻寬記憶體對於電腦使用者是個既熟悉又陌生的名詞,在顯示卡領域僅有少數高階版本採用,卻又對 AI 深度學習、高性能運算、網路等需要高頻寬、低功耗的應用環境提供不可或缺的效能表現。一般消費市場,最早由 AMD Radeon R9 Fury/R9 Nano 顯示卡搭載 HBM,由於 HBM 採用 interposer 與 GPU 封裝在同一基板(SiPs,System-in-Packages),省去在電路板的記憶體佈線,因此能夠做出如 Radeon R9 Nano 長度不到 160mm 的身材。

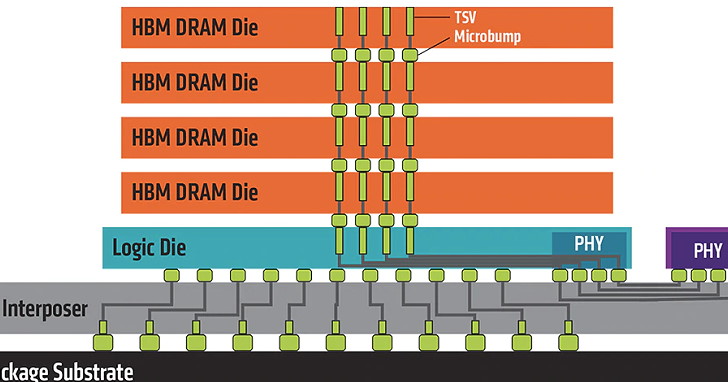

HBM 單一堆疊採用 1024bit 匯流排寬度,以 8 個 128bit 獨立通道所組成,可以堆疊 2~8 個記憶體晶粒,每個晶粒透過 TSV(Through Silicon Via)相互連接。每個晶粒可以提供 2Gb 容量,單一 pin 腳運作時脈為 500MHz,透過 DDR 技術達成 2 倍等效頻寬 1Gbps,單一 HBM 堆疊即可達成 128GB/s 存取頻寬。

▲HBM 透過 interposer 與其它具備記憶體控制器的晶粒相互連接,再封裝至基板。(圖片取自 AMD)

第二代 HBM 單一堆疊匯流排寬度依舊是 1024bit,由 8 個 128bit 通道所組成,但引進相當重要的 Pseudo Channel mode,能夠將 128bit 拆成 64bit+64bit 方式運作,這 2 個 64bit 通道共享命令通道,但內部 bank 與 I/O 資料通道則是相互分離,藉此達成各自獨立運作,能夠減少存取延遲。此時也藉由製程技術微縮,單一記憶體晶粒容量達到 8Gb,單一 pin 腳等效頻寬拉抬至 1.6Gbps~2Gbps。

近日 JEDEC 再次針對 HBM 規範 JESD235 文件進行更新,JESD235B HBM 單一堆疊匯流排還是 1024bit,但堆疊數量由 2、4、8 層再往上加入 4 層達 12 層,單一記憶體晶粒容量順勢推升至 16Gb,代表單一堆疊最大即可擁有 24GB 容量。單一 pin 腳時脈如今採用 1200MHz,透過 DDR 技術達成 2.4Gbps 等效頻寬。

資料來源

JEDEC Updates Groundbreaking High Bandwidth Memory (HBM) Standard

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!